威世合金电阻寄生电感的深度解析

威世合金电阻是一种大量的用于电子设备中的重要元件,性能直接影响到电路的稳定性和可靠性电子设计中,寄生电感是一个不容忽视的因素,可能会影响电阻的工作效率和电路的整体性能。本文将深入探讨威世合金电阻的寄生电感特性、对电路的影响。

1. 什么是寄生电感?

寄生电感是指在电路中,由于导体的几何形状和布局而产生的意外电感。是不可避免的,尤其是在高频电路中,寄生电感可能会显著影响信号的传输和电路的性能。

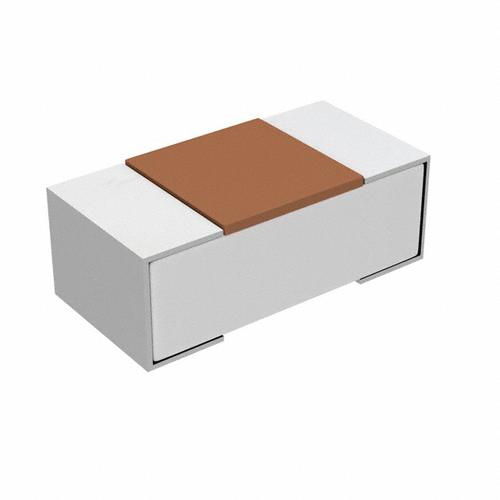

2. 威世合金电阻的基本特性

威世合金电阻主要由合金材料制成,能够优良的稳定性和低温系数。电阻值可精确控制,适用于各种精密电路。这些特性使得威世合金电阻成为高性能电子设备中的热门选择。

3. 寄生电感对威世合金电阻的影响

威世合金电阻的寄生电感会导致信号的延迟和失真,特别是在高频应用中。寄生电感的存在会与电阻的电阻值相互作用,形成一个复杂的阻抗特性,影响到电路的频率响应。

4. 如何测量寄生电感?

测量威世合金电阻的寄生电感可以使用网络分析仪或LCR表测试时,需要注意测试环境的影响,确保测量结果的准确性。选择适当的测试频率也非常的重要,因为寄生电感在不同频率下的表现可能会有所不同。

5. 减少寄生电感的方法

为了降低威世合金电阻的寄生电感,可以采取以下几种方法:

- **优化布局**:在电路设计中,合理安排电阻的位置,尽量减少导线的长度,以降低寄生电感。

- **使用屏蔽**:在高频应用中,使用屏蔽技术可以有效减少外部电磁干扰对电路的影响,从而降低寄生电感的影响。

- **选择合适的材料**:使用低寄生电感的电阻材料,可以在一定程度上降低寄生电感的影响。

6. 寄生电感的计算模型

设计电路时,理解寄生电感的计算模型非常的重要。通过电磁场理论,可以建立电阻的寄生电感模型,从而在设计阶段进行优化。这种模型包含了电阻的几何形状、材料特性和周围环境的影响。

7. 寄生电感的应用实例

现代电子设备中,威世合金电阻的寄生电感应用大量的。比如可以射频电路中,寄生电感会影响信号的完整性,这样看来设计工程师需要特别关注这一点高频开关电源中,寄生电感也会引发振荡和噪声问题,影响电源的稳定性。

8. 未来发展趋势

随着电子技术的不断进步,威世合金电阻的寄生电感问题将得到更多关注。未来,可能会出现更多先进的材料和设计方法,以进一步降低寄生电感的影响,提高电路的性能和可靠性。

威世合金电阻的寄生电感是一个在电子设计中不可忽视的因素。通过理解寄生电感的特性、对电路的影响,我们可以采取有效的措施来优化电路设计,提高电子设备的性能。随着技术的发展,未来我们将会看到更多创新的解决方案,以应对寄生电感带来的挑战。